Pendidikan teknik sering kali menjadi jembatan antara pengetahuan teoritis dan penerapan praktis. Seiring Anda maju dalam studi gelar Anda, Anda akan menemui desain sistem yang kompleks yang membutuhkan lebih dari sekadar kode atau diagram sirkuit. Di sinilah Bahasa Pemodelan Sistem (SysML) menjadi penting. SysML menyediakan cara standar untuk menggambarkan, menganalisis, merancang, dan memverifikasi sistem. Bagi mahasiswa universitas, mengadopsi bahasa ini sejak awal karier akademik Anda dapat secara signifikan meningkatkan kejelasan, pelacakan, dan keberhasilan proyek akhir Anda.

Panduan ini berfungsi sebagai referensi komprehensif. Ini mencakup komponen inti SysML, menjelaskan cara menerapkannya dalam pekerjaan akademik, dan menyoroti praktik terbaik untuk dokumentasi. Baik Anda merancang platform robotika, arsitektur perangkat lunak, atau perakitan mekanik, SysML menawarkan pendekatan terstruktur dalam rekayasa sistem.

Memahami Bahasa Pemodelan Sistem 🧩

SysML adalah bahasa pemodelan umum. Ini merupakan perluasan dari Bahasa Pemodelan Terpadu (UML), yang disesuaikan khusus untuk rekayasa sistem. Meskipun UML berfokus sangat kuat pada perangkat lunak dan desain berorientasi objek, SysML memperluas cakupan untuk mencakup perangkat keras, perangkat lunak, informasi, personel, dan prosedur. Dalam konteks akademik, fleksibilitas ini sangat penting karena proyek universitas sering melibatkan tim lintas disiplin.

Ketika Anda menggunakan SysML, Anda sedang membuat representasi visual dari suatu sistem. Model-model ini berfungsi sebagai bahasa bersama bagi para pemangku kepentingan. Mereka memungkinkan Anda untuk memvisualisasikan hubungan yang kompleks yang mungkin hilang dalam dokumentasi yang padat teks. Bahasa ini didasarkan pada diagram. Setiap jenis diagram memiliki tujuan khusus, menangkap aspek-aspek berbeda dari siklus hidup sistem.

Mengadopsi standar ini sejak awal membantu Anda mengembangkan pemikiran sistem. Ini mendorong Anda untuk mendefinisikan kebutuhan secara jelas sebelum langsung memulai implementasi. Disiplin ini mengurangi kesalahan di tahap pengembangan berikutnya dan memastikan bahwa produk akhir sesuai dengan niat awal.

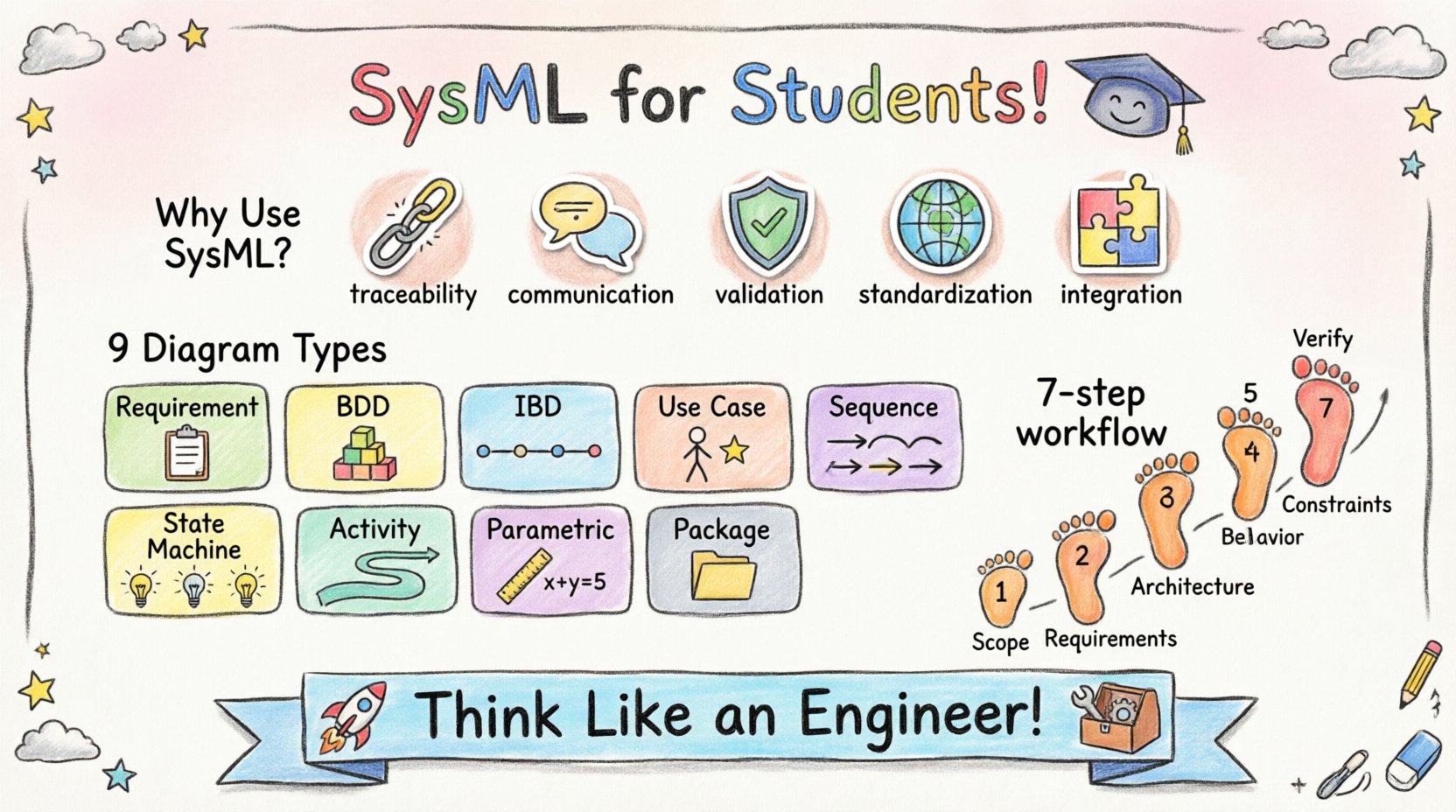

Mengapa Mahasiswa Harus Mengadopsi SysML 📈

Banyak mahasiswa bertanya-tanya apakah investasi waktu yang dibutuhkan untuk mempelajari bahasa pemodelan baru layak dilakukan. Jawabannya terletak pada kejelasan dan struktur yang dibawa oleh SysML untuk proyek-proyek yang kompleks. Berikut beberapa alasan mengapa SysML bermanfaat bagi pekerjaan tingkat universitas:

- Pelacakan: Anda dapat menghubungkan kebutuhan langsung ke elemen desain. Jika suatu kebutuhan berubah, Anda dapat langsung melihat bagian mana dari model yang terdampak.

- Komunikasi:Model visual lebih mudah dipahami oleh dosen dan mitra industri dibandingkan laporan teks yang padat. Mereka memberikan gambaran umum tingkat tinggi dari arsitektur.

- Validasi: Anda dapat memverifikasi bahwa desain sistem Anda benar-benar memenuhi batasan dan tujuan yang ditetapkan pada awal proyek.

- Standarisasi: SysML adalah standar internasional (ISO/IEC 19500). Menggunakannya menunjukkan kompetensi profesional kepada calon majikan di masa depan.

- Integrasi: Ini membantu mengintegrasikan komponen mekanik, listrik, dan perangkat lunak menjadi satu kesatuan yang utuh, yang merupakan hal umum dalam proyek rekayasa modern.

Dengan menggunakan SysML, Anda melampaui sketsa sembarangan. Anda menciptakan artefak yang terdokumentasi yang dapat ditinjau, dimodifikasi, dan digunakan kembali. Ini sangat berharga untuk proyek yang berlangsung selama satu semester di mana dokumentasi merupakan bagian penting dari kriteria penilaian.

Diagram Inti dan Aplikasinya 📊

SysML terdiri dari sembilan jenis diagram yang berbeda. Tidak setiap proyek membutuhkan semua jenis tersebut. Memahami kapan menggunakan setiap diagram merupakan keterampilan penting. Di bawah ini adalah penjelasan mengenai diagram utama dan penggunaannya secara khusus dalam proyek mahasiswa.

| Jenis Diagram | Fokus Utama | Kasus Penggunaan Umum |

|---|---|---|

| Diagram Kebutuhan | Kebutuhan Sistem | Menentukan kebutuhan fungsional dan non-fungsional. |

| Diagram Definisi Blok (BDD) | Struktur | Mendefinisikan bagian-bagian sistem dan hubungan antar mereka. |

| Diagram Blok Internal (IBD) | Koneksi Internal | Menunjukkan bagaimana bagian-bagian berinteraksi dan bertukar data. |

| Diagram Kasus Penggunaan | Interaksi | Mendeskripsikan bagaimana pengguna berinteraksi dengan sistem. |

| Diagram Urutan | Perilaku | Menunjukkan interaksi yang diurutkan menurut waktu antar bagian. |

| Diagram Mesin Status | Logika Status | Mendefinisikan bagaimana sistem bereaksi terhadap peristiwa seiring waktu. |

| Diagram Aktivitas | Alur Kerja | Memodelkan aliran kontrol atau data. |

| Diagram Parametrik | Kendala | Kendala matematis dan analisis kinerja. |

| Diagram Paket | Organisasi | Mengelompokkan elemen model menjadi kelompok-kelompok. |

Penjelasan Mendalam: Diagram Kebutuhan 📝

Diagram Kebutuhan sering menjadi titik awal untuk setiap proyek rekayasa. Diagram ini menangkap apa yang harus dilakukan oleh sistem. Dalam konteks universitas, hal ini sangat selaras dengan spesifikasi proyek yang diberikan oleh dosen atau klien.

Elemen-elemen kunci dalam diagram ini meliputi:

- Blok Kebutuhan: Ini mewakili kebutuhan tertentu. Misalnya, “Robot harus mampu mengangkat 5kg” atau “Waktu respons perangkat lunak harus di bawah 100ms”.

- Kendala: Ini menentukan batasan pada kebutuhan. Anda mungkin menentukan bahwa suatu komponen harus beroperasi dalam rentang suhu tertentu.

- Hubungan:SysML memungkinkan Anda untuk menghubungkan persyaratan. Anda dapat menentukan apakah satu persyaratan memenuhi persyaratan lain, atau apakah suatu persyaratan direfinement menjadi sub-persyaratan.

Pelacakan adalah aspek paling penting di sini. Anda harus menghubungkan setiap persyaratan ke elemen desain. Jika suatu persyaratan tidak dihubungkan ke apa pun dalam model Anda, maka dianggap “terlantar.” Persyaratan yang terlantar menunjukkan pekerjaan desain yang belum lengkap. Selama pertahanan proyek Anda, dosen akan mencari tautan-tautan ini untuk memverifikasi bahwa Anda telah menangani setiap spesifikasi.

Penjelasan Mendalam: Diagram Struktur 🧱

Setelah persyaratan ditentukan, Anda perlu menentukan struktur sistem. SysML menawarkan dua diagram utama untuk tujuan ini: Diagram Definisi Blok (BDD) dan Diagram Blok Internal (IBD).

Diagram Definisi Blok (BDD)

BDD mendefinisikan hierarki sistem. Diagram ini memecah sistem menjadi blok-blok. Sebuah blok dapat mewakili bagian fisik, modul perangkat lunak, atau fungsi logis. Diagram ini pada dasarnya adalah diagram kelas yang disesuaikan untuk sistem.

Ketika membuat BDD untuk proyek kampus:

- Tentukan blok tingkat atas sebagai sistem Anda.

- Buat blok anak untuk subsistem. Untuk proyek drone, Anda mungkin memiliki blok untuk “Sistem Daya”, “Unit Kontrol”, dan “Propulsi”.

- Tentukan antarmuka. Antarmuka mendefinisikan bagaimana blok-blok berkomunikasi tanpa mengetahui detail internal blok lainnya.

Diagram Blok Internal (IBD)

IBD memfokuskan pada blok tertentu untuk menunjukkan komposisi internalnya. Diagram ini mengungkap bagaimana bagian-bagian internal saling terhubung.

- Port: Ini adalah titik koneksi pada suatu blok. Mereka menentukan di mana data atau sinyal masuk atau keluar.

- Aliran: Ini mewakili pergerakan data, material, atau energi antar port.

- Properti: Ini mendefinisikan variabel atau komponen internal dalam blok.

Tingkat detail ini sangat penting untuk proyek lintas disiplin. Ini membantu insinyur mesin memahami dari mana sinyal listrik berasal, dan insinyur perangkat lunak memahami batasan fisik.

Penjelasan Mendalam: Diagram Perilaku ⚙️

Struktur mendefinisikan apa yang menjadi sistem. Perilaku mendefinisikan apa yang dilakukan sistem. SysML menyediakan beberapa diagram untuk menangkap perilaku seiring waktu.

Diagram Kasus Penggunaan

Diagram ini berfokus pada perspektif pengguna. Diagram ini mengidentifikasi aktor (pengguna atau sistem eksternal) dan kasus penggunaan (tindakan) yang mereka lakukan. Diagram ini sangat baik untuk menentukan cakupan proyek Anda. Jika suatu tindakan tidak ada dalam kasus penggunaan, kemungkinan besar berada di luar cakupan.

Diagram Urutan

Diagram urutan menunjukkan interaksi secara kronologis. Diagram ini sangat ideal untuk menjelaskan bagaimana suatu fungsi tertentu bekerja.

- Mereka menunjukkan objek (atau blok) sebagai garis vertikal.

- Pesan ditampilkan sebagai panah horizontal di antara garis-garis tersebut.

- Anda dapat memodelkan lingkaran umpan balik dan penanganan kesalahan.

Untuk proyek yang berat perangkat lunak, diagram ini membantu memvalidasi alur logika sebelum menulis kode. Untuk proyek perangkat keras, diagram ini dapat memodelkan pertukaran sinyal antar komponen.

Diagram Mesin Status

Beberapa sistem memiliki keadaan yang berbeda. Lampu lalu lintas, terminal pembayaran, atau lengan robotik dalam mode “Diam” vs “Bergerak” adalah contohnya. Diagram Mesin Status memetakan keadaan-keadaan ini dan transisi antar keduanya.

- Keadaan:Kondisi saat sistem melakukan suatu tindakan atau menunggu suatu peristiwa.

- Transisi:Pemicu yang memindahkan sistem dari satu keadaan ke keadaan lain.

- Peristiwa:Pemicu yang menyebabkan transisi.

Ini sangat penting untuk sistem tertanam dan logika kontrol. Ini mencegah kondisi persaingan dan memastikan sistem berperilaku dapat diprediksi di semua kondisi.

Penjelasan Mendalam: Diagram Parametrik 📐

Diagram parametrik unik untuk SysML dan sangat dihargai dalam kurikulum teknik. Mereka memungkinkan Anda memodelkan batasan dan melakukan analisis.

Anda dapat menentukan persamaan langsung dalam model. Sebagai contoh, Anda dapat menghubungkan properti “Tegangan” dari blok daya dengan properti “Arus” dari blok beban menggunakan Hukum Ohm. Ini memungkinkan validasi kinerja dini.

Manfaatnya meliputi:

- Verifikasi:Anda dapat memeriksa apakah pilihan desain memenuhi batas fisik.

- Analisis Pertukaran:Anda dapat menyesuaikan parameter untuk melihat bagaimana dampaknya terhadap kinerja keseluruhan sistem.

- Dokumentasi:Ini mendokumentasikan dasar matematis dari keputusan desain Anda.

Meskipun tidak setiap proyek membutuhkan matematika yang rumit, termasuk batasan parametrik menunjukkan tingkat ketelitian teknik yang tinggi.

Membangun Model: Alur Kerja Langkah demi Langkah 🛠️

Membuat model SysML bisa terasa menakutkan. Alur kerja yang terstruktur membantu mengelola kompleksitas. Ikuti urutan ini untuk proyek kampus Anda:

- Tentukan Lingkup:Buat Diagram Kasus Penggunaan untuk menetapkan batas. Identifikasi aktor utama dan fungsi-fungsinya.

- Tangkap Kebutuhan:Buat Diagram Kebutuhan. Daftar semua kebutuhan fungsional dan non-fungsional. Pastikan mereka spesifik dan dapat diukur.

- Kembangkan Arsitektur:Buat Diagram Definisi Blok. Pisahkan sistem menjadi subsistem yang dapat dikelola. Tentukan antarmuka di antara mereka.

- Rincian Struktur Internal:Gunakan Diagram Blok Internal untuk menunjukkan koneksi pada subsistem penting. Tentukan port dan aliran.

- Model Perilaku: Gunakan diagram Urutan dan Mesin Status untuk menjelaskan bagaimana sistem bereaksi terhadap input dan peristiwa.

- Terapkan Kendala: Jika berlaku, tambahkan diagram Parametrik untuk memvalidasi metrik kinerja.

- Verifikasi Jejak Kembali: Periksa bahwa setiap kebutuhan terhubung ke elemen desain. Pastikan tidak ada kebutuhan yang terpisah.

Proses iteratif ini memungkinkan Anda menyempurnakan model seiring Anda mempelajari sistem lebih lanjut. Jangan mencoba membuat model sempurna dalam satu kali langkah. Mulailah dari dasar-dasar dan tambahkan detail sebanyak yang diperlukan.

Kesalahan Umum yang Harus Dihindari 🚫

Siswa sering membuat kesalahan yang dapat diprediksi saat memodelkan. Kesadaran terhadap hal ini dapat menghemat waktu Anda selama tahap penilaian.

- Over-Modeling: Mencoba memodelkan setiap detail dapat membuat diagram menjadi kusut. Fokus pada arsitektur tingkat tinggi terlebih dahulu. Hanya rinci bagian yang diperlukan untuk kejelasan.

- Referensi Melingkar: Pastikan tautan jejak kembali Anda tidak membentuk lingkaran. Kebutuhan tidak boleh merujuk pada elemen desain yang kembali merujuk ke kebutuhan yang sama secara melingkar.

- Antarmuka yang Hilang: Jelaskan dengan jelas bagaimana blok berkomunikasi. Jika sebuah blok mengirim data ke blok lain, harus ada antarmuka atau port yang didefinisikan.

- Mengabaikan Kendala: Jangan biarkan kebutuhan kinerja hanya sebagai teks. Jika Anda memiliki kendala numerik, modelkan dalam diagram Parametrik jika memungkinkan.

- Penamaan yang Tidak Konsisten: Gunakan konvensi penamaan yang konsisten di seluruh model. Blok yang bernama “Sensor” tidak boleh disebut sebagai “Pengumpul Data” di diagram lain.

Kiat untuk Keberhasilan Akademik 💡

Ketika mempresentasikan model SysML Anda kepada dosen atau dalam tesis, pertimbangkan hal-hal berikut:

- Jaga Kebersihan: Hindari garis yang saling bersilangan dan tata letak yang berantakan. Gunakan paket untuk mengatur model yang kompleks menjadi bagian-bagian yang mudah dibaca.

- Tambahkan Anotasi: Gunakan catatan untuk menjelaskan keputusan yang kompleks. Diagram adalah alat bantu visual, tetapi terkadang teks diperlukan untuk konteks.

- Ekspor dengan Benar: Banyak alat memungkinkan Anda mengekspor diagram ke PDF atau gambar. Pastikan resolusi cukup tinggi untuk laporan cetak.

- Fokus pada Logika: Dosen kurang tertarik pada estetika dan lebih tertarik pada logika. Apakah model tersebut secara akurat merepresentasikan sistem?

- Kontrol Versi: Jika Anda menggunakan alat yang mendukungnya, lacak versi model. Ini membantu mendokumentasikan evolusi desain Anda.

Integrasi dengan Disiplin Teknik Lainnya 🔗

SysML bukan hanya untuk insinyur mekanik atau perangkat lunak. Ini menghubungkan celah antar disiplin. Dalam tim multidisiplin, model berfungsi sebagai satu-satunya sumber kebenaran.

Sebagai contoh, dalam proyek mekatronika:

- Insinyur mekanik menentukan blok fisik dan dimensi dalam BDD.

- Insinyur listrik menentukan antarmuka daya dan sinyal.

- Insinyur perangkat lunak menentukan logika menggunakan Mesin Status.

Semua pandangan ini terintegrasi ke dalam satu model. Ini mengurangi risiko desain yang tidak kompatibel. Ini memastikan bahwa logika perangkat lunak sesuai dengan sinyal listrik, yang sesuai dengan gerakan mekanik.

Dokumentasi dan Pelaporan 📄

Proyek akademik membutuhkan dokumentasi yang luas. Model SysML dapat digunakan langsung untuk menghasilkan laporan. Banyak lingkungan pemodelan memungkinkan Anda menghasilkan dokumentasi yang mengekstrak informasi dari model.

Bagian penting yang harus disertakan dalam laporan Anda berdasarkan model:

- Gambaran Sistem:Gunakan BDD untuk menunjukkan arsitektur.

- Analisis Kebutuhan:Gunakan Diagram Kebutuhan untuk menunjukkan pelacakan.

- Desain Fungsional:Gunakan diagram Urutan dan Aktivitas untuk menjelaskan alur kerja.

- Kontrol Antarmuka:Gunakan IBD untuk menjelaskan koneksi.

Menghasilkan teks dari model memastikan konsistensi. Jika Anda memperbarui model, dokumentasi juga akan diperbarui. Ini mengurangi kemungkinan laporan Anda bertentangan dengan desain Anda.

Pikiran Akhir tentang Berpikir Sistem 🌍

Memahami SysML bukan hanya tentang menggambar diagram. Ini tentang mengembangkan pola pikir. Anda belajar memikirkan sistem secara holistik. Anda mempertimbangkan input, output, kendala, dan interaksi. Perspektif ini sangat dihargai di industri.

Saat Anda mengerjakan proyek kampus Anda, anggap model sebagai dokumen hidup. Model harus berkembang seiring Anda belajar. Jangan takut untuk merefaktor model Anda. Tujuannya adalah kejelasan dan pemahaman, bukan kesempurnaan pada percobaan pertama. Dengan menguasai teknik pemodelan ini, Anda sedang mempersiapkan diri untuk kompleksitas rekayasa modern.

Mulai kecil. Tentukan kebutuhan Anda dengan jelas. Bangun struktur Anda. Verifikasi perilaku Anda. Dengan latihan, SysML akan menjadi alat yang tak tergantikan dalam peralatan rekayasa Anda. Ini memberikan struktur yang diperlukan untuk mengubah ide-ide kompleks menjadi kenyataan yang fungsional.